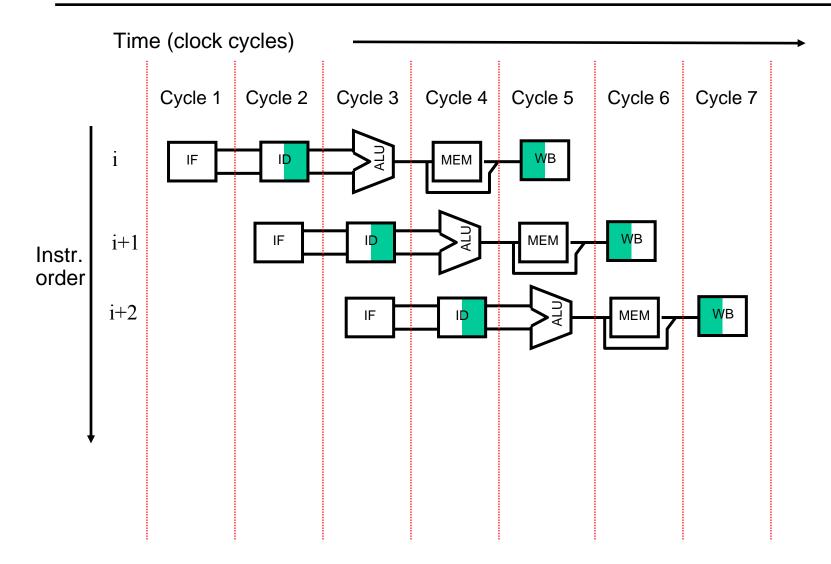

### Recap

- Computers execute billions of instructions, so instruction throughput is what matters

- Main idea behind pipelining: Divide instruction execution across several stages

- each stage accesses only a subset of the CPU's resources

- Example: Classic 5-stage RISC pipeline

- IF ID EX MEM WB

- Simultaneously have different instructions in different stages

- Ideally, can issue a new instruction every cycle

## Recap (Cont'd)

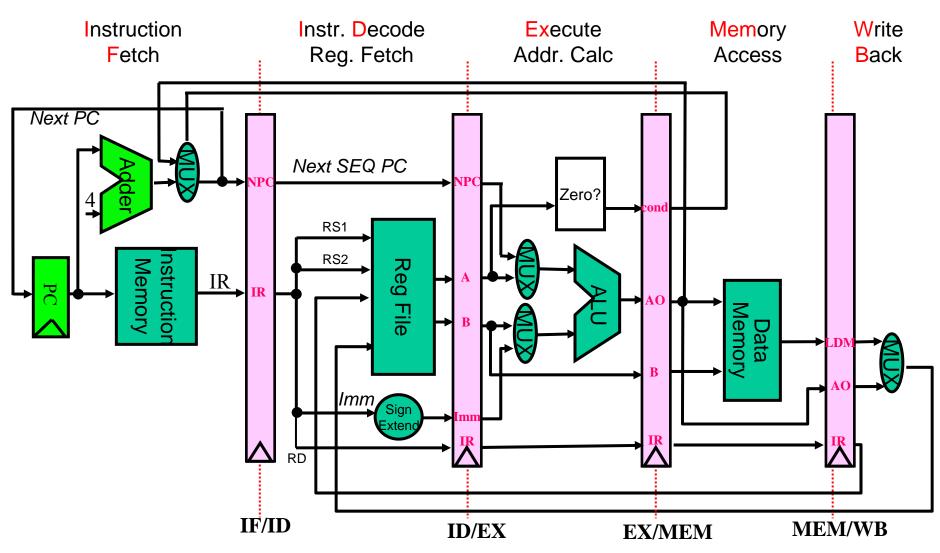

## Pipelined Implementation of a RISC ISA

2/1/2006

# Pipeline stage: Instruction Fetch (IF)

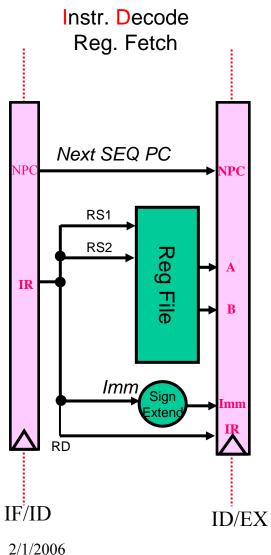

#### Pipeline stage: Instruction Decode (ID)

ID/EX.A ← Regs[IF/ID.IR[rs]]; ID/EX.B ← Regs[IF/ID.IR[rt]; ID/EX.NPC←IF/ID.NPC;  $ID/EX.IR \leftarrow IF/ID.IR;$ ID/EX.Imm ← sign-extend (IF/ID.IR[immediate field])

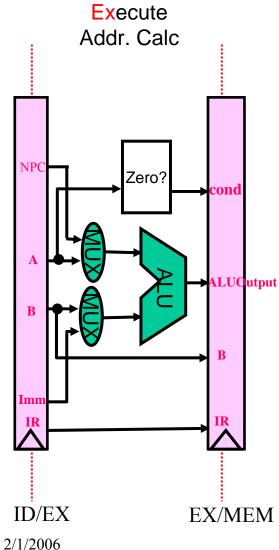

## Pipeline stage: Execute (EX)

**ALU instruction** EX/MEM.IR  $\leftarrow$  ID/EX.IR;

EX/MEM.ALUOutput ← ID/EX.A func ID/EX.B; or

EX/MEM.ALUOutput ← ID/EX.A op ID/EX.Imm;

**Branch instruction** EX/MEM.ALUOutput ← ID/EX.NPC + (ID/EX.Imm <<2);

$EX/MEM.cond \leftarrow$ (ID/EX.A == 0);

Load/store instruction  $EX/MEM.IR \leftarrow ID/EX.IR;$

EX/MEM.ALUOutput ← ID/EX.A + ID/EX.Imm;

$EX/MEM.B \leftarrow ID/EX.B;$

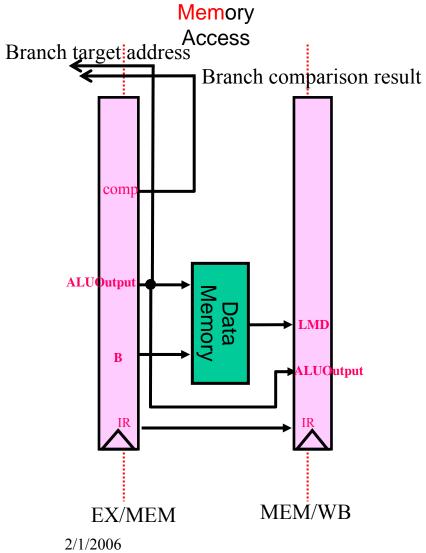

Pipeline stage: Memory access (MEM)

ALU instruction MEM/WB.IR←EX/MEM.IR; MEM.WB.ALUOutput ← EX/MEM.ALUOutput;

Load/store instruction MEM/WB.IR←EX/MEM.IR;

MEM/WB.LMD ← Mem[EX/MEM.ALUOutput]; or Mem[EX/MEM.ALUOutput] ← EX/MEM.B;

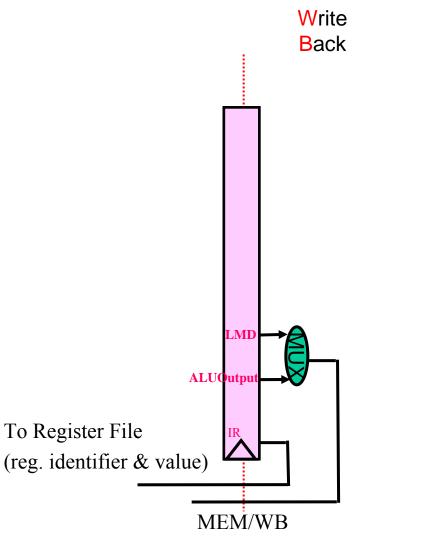

# Pipeline stage: Write Back (WB)

ALU instruction Regs[MEM/WB.IR[rd]]← MEM.WB.ALUOutput; or Regs[MEM/WB.IR[rt]]← MEM.WB.ALUOutput;

Load instruction only Regs[MEM/WB.IR[rt]]← MEM/WB.LMD

## **Pipeline Hazards**

- Should we expect a CPI of 1 in practice?

- Unfortunately, the answer to the question is NO.

- Limit to pipelining: Hazards

- Prevent next instruction from executing during its designated clock cycle

- Three classes of hazards

- Structural: Hardware cannot support this combination of instructions two instructions need the same resource.

Data: Instruction depends on result of prior instruction still in the pipeline Control: Pipelining of branches & other instructions that change the PC

- Common solution is to stall the pipeline until the hazard is resolved, inserting one or more "bubbles" in the pipeline

- To do this, hardware or software must detect that a hazard has occurred

## Pipeline Hazards (A): Structural Hazards

- Occur when two or more instructions need the same resource

- Common methods for eliminating structural hazards are:

- Duplicate resources

- Pipeline the resource

- Reorder the instructions

- It may be too expensive to eliminate a structural hazard, in which case the pipeline should stall

- no new instructions are issued until the hazard has been resolved

- What are some examples of structural hazards?

#### One Memory Port Structural Hazard

2/1/2006

# Pipeline Speedup Example: One or Two Memory Ports

- Two machines

- Machine A: Dual ported memory

- Machine B: Single ported memory, but its pipelined implementation has a clock rate that is 1.05 times faster

- Ideal CPI = 1 for both

- Loads are 40% of instructions executed (cause stalls in machine B)

- Which is faster?

| Speedup =            | $= \frac{\text{Ideal CPI} \times \text{Pipeline depth}}{\text{Ideal CPI} + \text{Pipeline stall CPI}} \times \frac{\text{Cycle Time}_{\text{unpipelined}}}{\text{Cycle Time}_{\text{pipelined}}}$ |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Speedup <sub>A</sub> | = (Pipeline Depth/ $(1 + 0)$ ) x 1                                                                                                                                                                |  |  |  |  |  |  |

|                      | = Pipeline Depth                                                                                                                                                                                  |  |  |  |  |  |  |

| Speedup <sub>B</sub> | $p_B = (Pipeline Depth/(1 + 0.4 x 1)) x 1.05$                                                                                                                                                     |  |  |  |  |  |  |

|                      | = 0.75  x Pipeline Depth                                                                                                                                                                          |  |  |  |  |  |  |

|                      | = Pipeline Depth<br>= (Pipeline Depth/ $(1 + 0.4 \times 1)$ ) x 1.05                                                                                                                              |  |  |  |  |  |  |

Machine A is 1.33 times faster

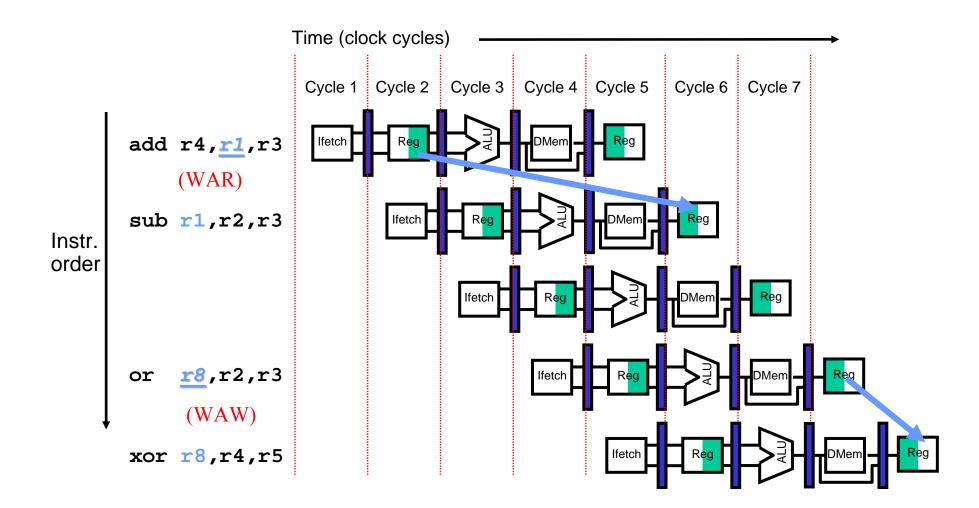

#### Pipeline Hazards (B): Data Hazards

Three generic types of data hazards

- Read After Write (RAW)

- $Instr_J$  tries to read operand before  $Instr_I$  (I < J) writes it

- Called a dependence

- Write After Read (WAR)

- Instr<sub>J</sub> writes operand before Instr<sub>I</sub> reads it

- Called an anti-dependence

- Name dependence (renaming)

- No value being transmitted

- Write After Write (WAW)

- Instr<sub>J</sub> writes operand before Instr<sub>I</sub> writes it

- Called an output dependence

- Name dependence (renaming)

- No value being transmitted

I: add r1,r2,r3

J: sub r4,r1,r3

I: sub r1,r4,r3 J: add r1,r2,r3

# Data Hazards and Pipeline Stalls

- Do all kinds of data hazards translate into pipeline stalls?

- NO, whether or not a data hazard results in a stall depends on the pipeline structure

- For the simple five-stage RISC pipeline

- Only RAW hazards result in a pipeline stall

- Instruction reading a register needs to wait until it is written

- WAR and WAW hazards cannot occur because

- All instructions take 5 stages

- Reads happen in the 2<sup>nd</sup> stage (ID)

- Writes happen in the 5<sup>th</sup> stage (WB)

- No way for a write from a subsequent instruction to interfere with the read (or write) of a prior instruction

- For more complicated pipelines (later in the course)

- Both WAR and WAW hazards are possible if instructions execute out of order or access (read) data later in the pipeline

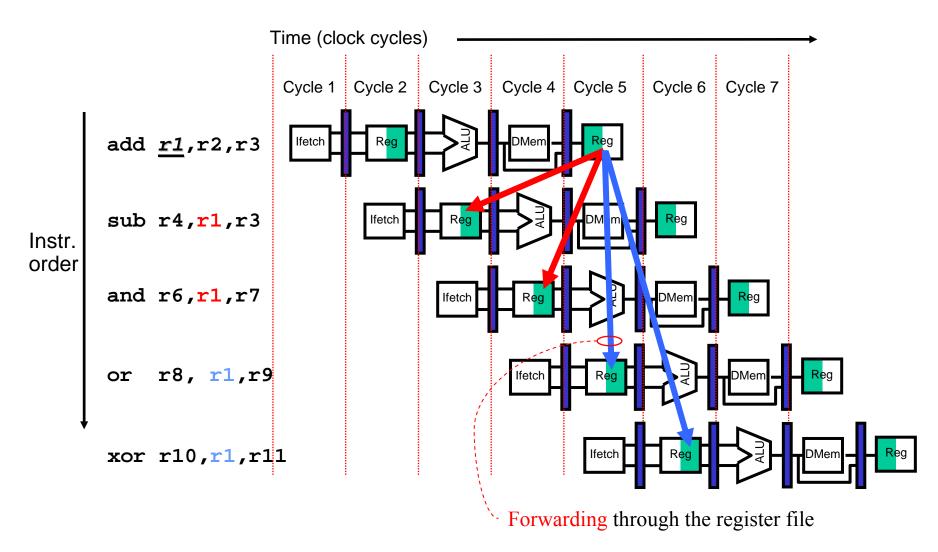

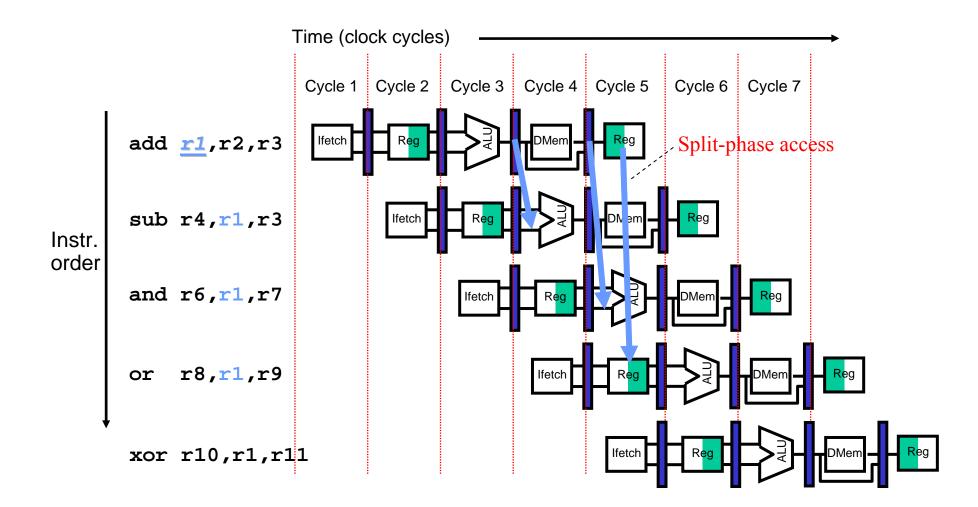

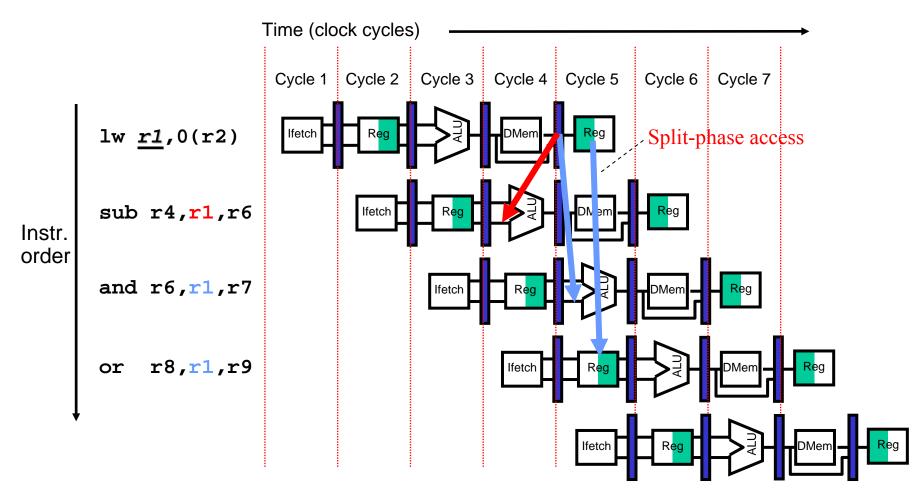

## RAW Hazards in the 5-stage Pipeline

#### Absence of WAR and WAW Hazards

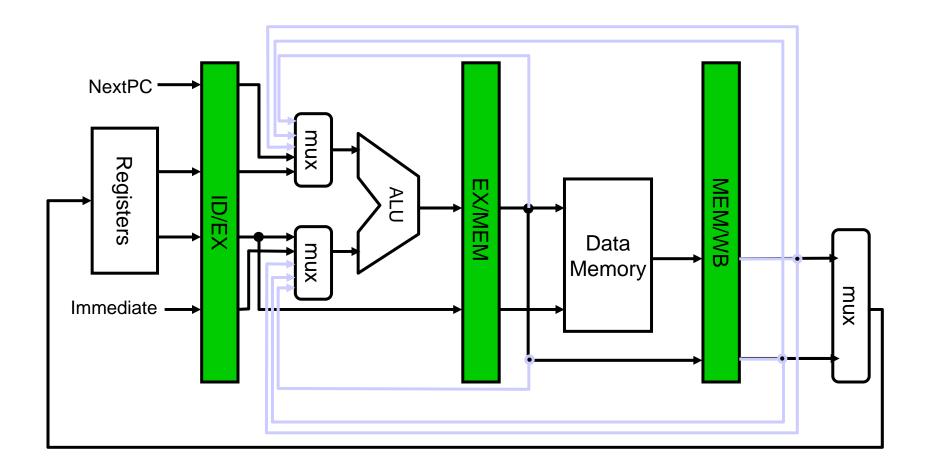

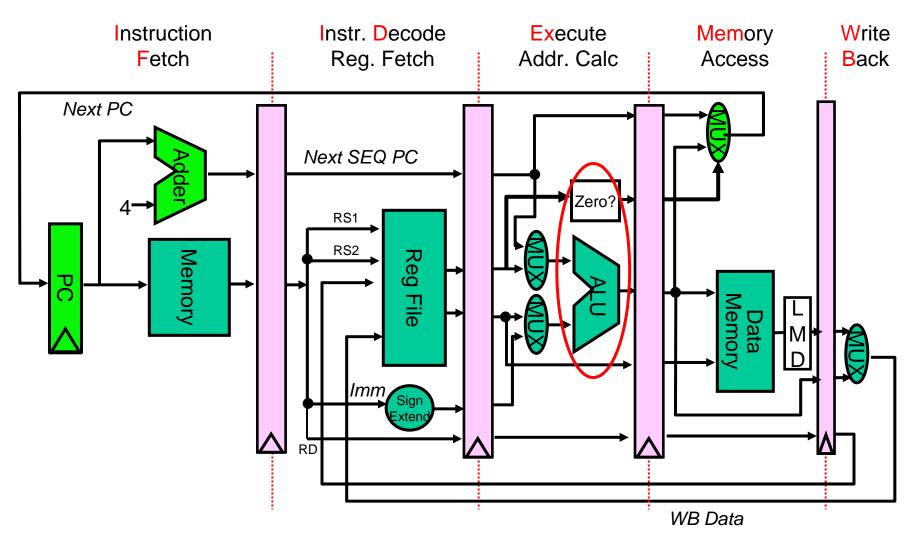

# Reducing Impact of RAW Hazards: Data Forwarding

- Data forwarding (also called bypassing or short-circuiting)

- Directly transfers data from each stage to earlier pipeline stages

- Result is accessible before it gets written into the register file.

| Instri: add r1,r2,r3 | (result ready after EX stage) |  |  |  |

|----------------------|-------------------------------|--|--|--|

|                      |                               |  |  |  |

| Instrj: sub r4,r1,r5 | (result needed in EX stage)   |  |  |  |

- To support data forwarding, additional hardware is required.

- Multiplexers to allow data to be transferred back

- Control logic for the multiplexers

#### Avoidance of RAW Hazards Using Forwarding

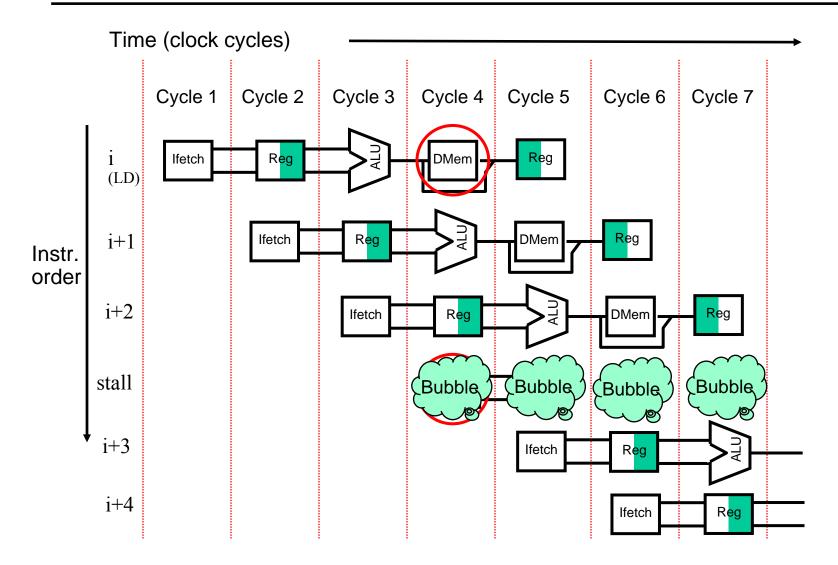

### Forwarding Does Not Eliminate All Hazards

Cope with this by stalling the EXE stage till results are available

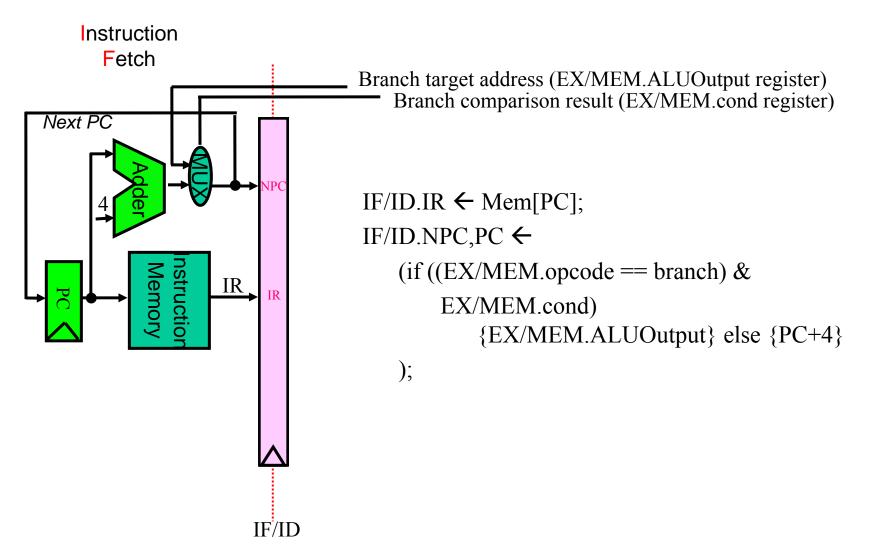

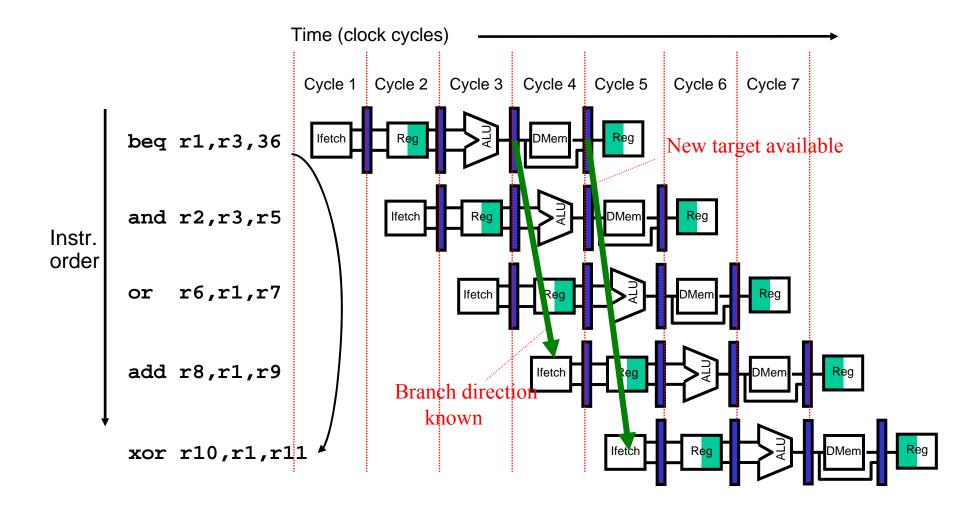

# Pipeline Hazards (C): Control Hazards

- Control hazards occur due to instructions changing the PC

- can result in a large performance loss

- A branch is either

- Taken:  $PC \leftarrow PC + Imm$

- Not Taken:  $PC \leftarrow PC + 4$

- Cannot fetch the next instruction till value of PC is known

- Simplest solution is to stall the pipeline upon detecting a branch

- ID stage detects the branch

- Don't know if the branch is taken until the EX stage

- New PC is not changed until the end of the MEM stage, after determining if the branch is taken and the new PC value

- If the branch is taken, we need to repeat some stages and fetch new instructions

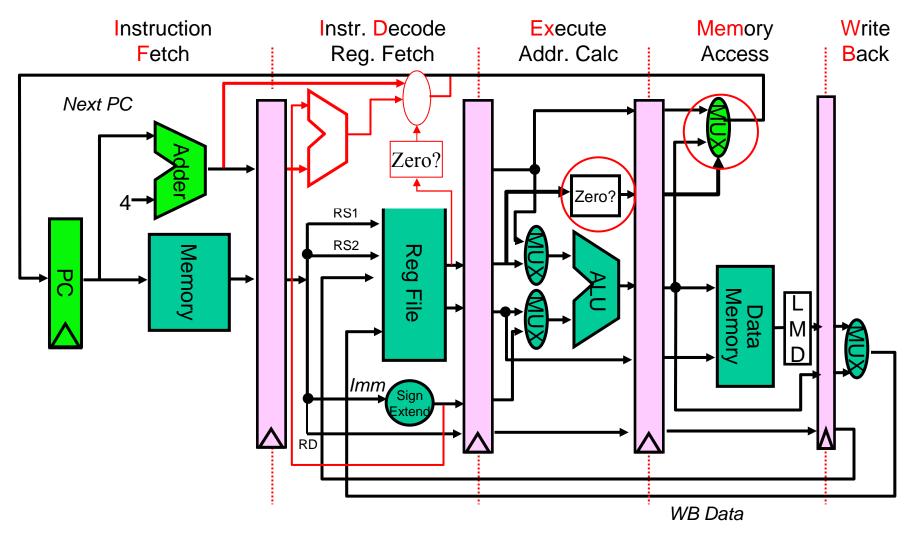

## (Review) Pipelined Implementation of a RISC ISA

#### 3 Cycle Stall on Branch-Induced Control Hazards

#### Impact of Branch Stalls

- If CPI = 1, 30% branches

- Stall 3 cycles => new CPI = (1 + 0.3\*3) = 1.9!

- 50% of these branches taken => new CPI = 1 + 0.15\*3 + 0.15\*2 = 1.7

- Penalty would be worse for current-day (longer) pipelines

- IF and ID-like stages are each multiple-cycle

- How do we reduce impact of branch stalls?

- Two part solution:

- Determine branch taken or not sooner, AND

- Compute taken branch address earlier

# Pipelined Implementation of a RISC ISA: Reducing Branch Penalty to 1 cycle

2/1/2006

## Branch Behavior in Programs

- Based on SPEC benchmarks on DLX (CA-AQA, 2<sup>nd</sup> Edition)

- Branches occur with a frequency of 14% to 16% in integer programs and 3% to 12% in floating point programs.

- About 75% of the branches are forward branches

- 60% of forward branches are taken

- 80% of backward branches are taken

- Why are branches (especially backward branches) more likely to be taken than not taken?

## Dealing with Branch Stalls

- Approach 1: Stall until branch direction is clear

- Approach 2: Predict Branch Not Taken

- Execute successor instructions in sequence

- PC+4 already calculated, so use it to get next instruction; chances are the branch is not taken

- "Squash" instructions in pipeline if branch actually taken

- Can do this because CPU state not updated till late in the pipeline

|                | Clock Number |    |      |      |      |      |     |     |    |

|----------------|--------------|----|------|------|------|------|-----|-----|----|

| Instr.         | 1            | 2  | 3    | 4    | 5    | 6    | 7   | 8   | 9  |

| i ( <b>T</b> ) | IF           | ID | EX   | MEM  | WB   |      |     |     |    |

| i+1            |              | IF | idle | idle | idle | idle |     |     |    |

| Т              |              |    | IF   | ID   | EX   | MEM  | WB  |     |    |

| T+1            |              |    |      | IF   | ID   | EX   | MEM | WB  |    |

| T+2            |              |    |      |      | IF   | ID   | EX  | MEM | WB |

## Dealing with Branch Stalls (cont'd)

- Approach 3: Predict Branch Taken

- Most branches are taken

- But haven't yet calculated target address in a 5-stage RISC pipeline

- So, will still incur a 1-cycle latency

- Makes sense on machines where branch target is known before outcome

- (later: Branch Target Buffers)

- Approach 4: Delayed Branch

- Define branch to take place AFTER n following instructions branch instruction sequential successor<sub>1</sub> sequential successor<sub>2</sub> ..... sequential successor<sub>n</sub>

n branch delay slots

branch target if taken

# Branch Delay Slots

• Instructions in the branch delay slot(s) get executed whether or not branch is taken

|                | Clock Number |    |    |     |     |     |     |     |    |

|----------------|--------------|----|----|-----|-----|-----|-----|-----|----|

| Instr.         | 1            | 2  | 3  | 4   | 5   | 6   | 7   | 8   | 9  |

| i ( <b>T</b> ) | IF           | ID | EX | MEM | WB  |     |     |     |    |

| D(i+1)         |              | IF | ID | EX  | MEM | WB  |     |     |    |

| Т              |              |    | IF | ID  | EX  | MEM | WB  |     |    |

| T+1            |              |    |    | IF  | ID  | EX  | MEM | WB  |    |

| T+2            |              |    |    |     | IF  | ID  | EX  | MEM | WB |

- Heavily used in early RISC machines

- 1 delay-slot suffices for a 5-stage pipeline (target available at end of ID)

- Machines with deep pipelines require additional delay slots to avoid branch penalties

- Benefits are unclear

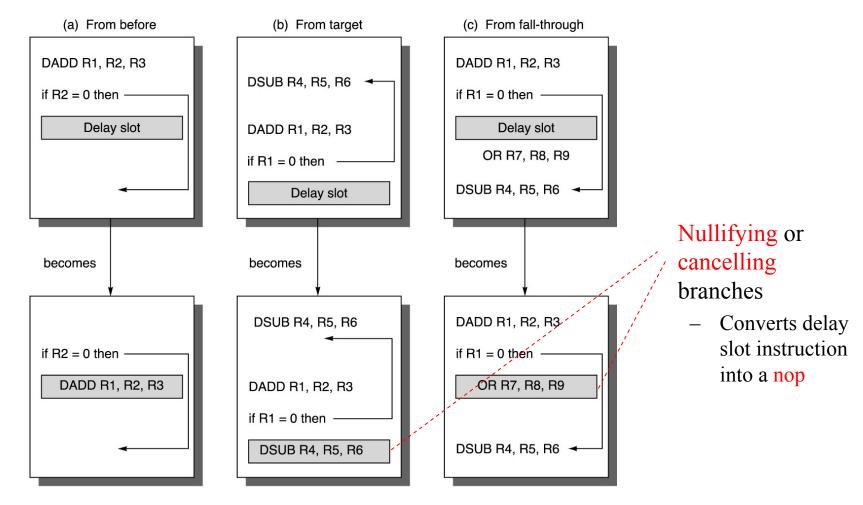

## Scheduling the Branch Delay Slot

Where does the instruction for the delay slot come from?

## **Evaluating Branch Alternatives**

Pipeline speedup =  $\frac{\text{Pipeline depth}}{1 + \text{Branch frequency} \times \text{Branch penalty}}$

- Assumptions

- 14% of instructions are branches

- 30% of branches are not taken

- 50% of delay slots can be filled with useful instructions

| Scheduling          | Branch  | CPI  | speedup v.<br>unpipelined | speedup v. |

|---------------------|---------|------|---------------------------|------------|

| scheme              | penalty |      | unpipelined               | stall      |

| Slow stall pipeline | 3       | 1.42 | 3.5                       | 1.0        |

| Fast stall pipeline | 1       | 1.14 | 4.4                       | 1.26       |

| Predict taken       | 1       | 1.14 | 4.4                       | 1.26       |

| Predict not taken   | 0.7     | 1.10 | 4.5                       | 1.29       |

| Delayed branch      | 0.5     | 1.07 | 4.7                       | 1.34       |

• A compiler can reorder instructions to further improve speedup

# Importance of Avoiding Branch Stalls

- Crucial in modern microprocessors, which issue/execute multiple instructions every cycle

- Need to have a steady stream of instructions to keep the hardware busy

- Stalls due to control hazards dominate

- So far, we have looked at static schemes for reducing branch penalties

- Same scheme applies to every branch instruction

- Potential for increased benefits from dynamic schemes

- Can choose most appropriate scheme separately for each instruction

- Branches to top of loop have different behavior (Taken) than "if (x == 0) return;" (Not Taken)

- Can "learn" appropriate scheme based on observed behavior

- Dynamic (hardware) branch prediction schemes

- For both direction (T or NT) and target prediction

- Key element of all modern microprocessors